Description

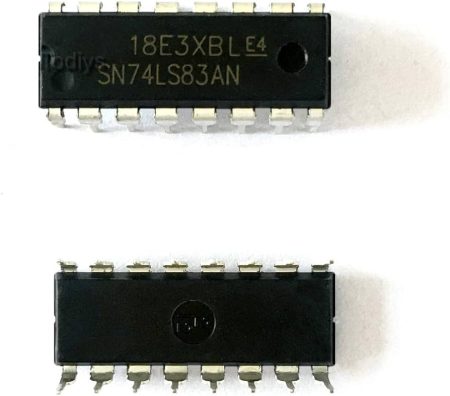

- Les sorties de somme (Σ) sont fournies pour chaque bit, et la retenue résultante (C4) est obtenue à partir du quatrième bit.

- Cet additionneur dispose d’une anticipation interne complète sur les quatre bits, générant le terme de retenue en 10 ns généralement. Cette capacité offre des performances d’anticipation partielles en termes d’économie pour les concepteurs de systèmes.

- La logique de l’additionneur, y compris le report, est implémentée sous sa vraie forme. Le report de bout en bout peut être accompli sans avoir besoin de logique ou d’inversion de niveau.

- Les systèmes atteignent des performances d’anticipation partielles avec l’économie du report d’ondulation.

- Tension d’alimentation et mise à la terre sur les broches d’angle pour simplifier la disposition des cartes de circuits imprimés.

- Ce composant appartient à la famille 74LS et est disponible dans un boîtier DIP-16.

- La plage de tension d’alimentation est de 4,75 V à 5,25 V.

- Le temps de propagation est de 16 ns